Publications

Title: HfO2-based ferroelectric synaptic devices: challenges and engineering solutions

Authors : Taegyu Kwon, Hyeong Seok Choi, Dong Hyun Lee, Dong Hee Han, Yong Hyeon Cho, Intak Jeon, Chang Hwa Jung, Hanjin Lim, Taehwan Moon and Min Hyuk Park

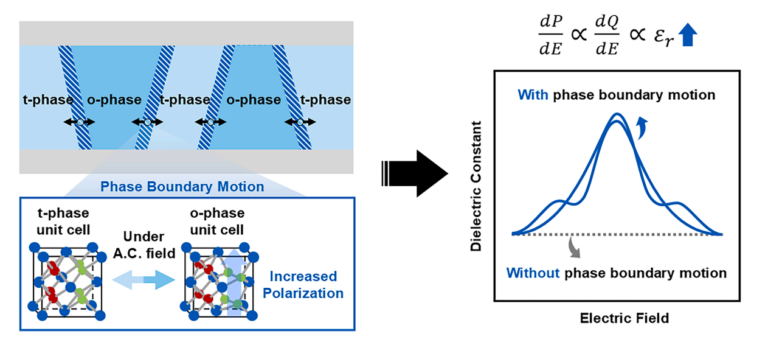

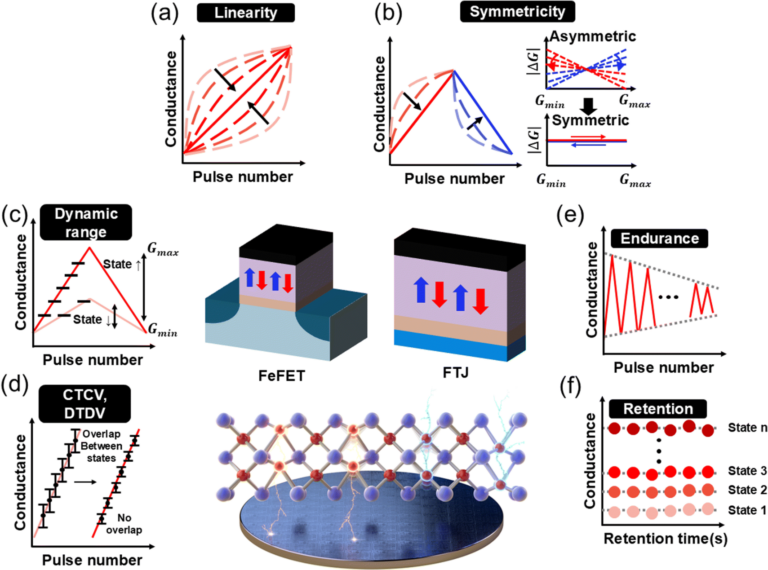

Abstract: HfO2-based ferroelectric memories have garnered significant attention for their potential to serve as artificial synaptic devices owing to their scalability and CMOS compatibility. This review examines the key material properties and challenges associated with HfO2-based ferroelectric artificial synaptic devices as well as the recent advancements in engineering strategies to improve their synaptic performance. The fundamental physics and material properties of HfO2-based ferroelectrics are reviewed to understand the theoretical origin of the aforementioned technical issues in ferroelectric HfO2-based synaptic devices. Based on the understanding, strategies to resolve the various technical issues from the device to array level are discussed, along with reviewing important progresses in recent studies. Based on these recent technical advancements, new perspectives to achieve high performance and highly reliable HfO2-based ferroelectric synaptic devices and their array are provided.

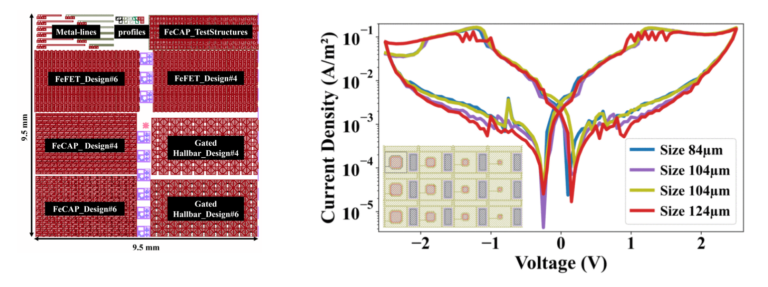

Authors : Anwesha Panda, Alexander Flasby, Yanming Zhang, Simon Mellaerts, Wei Fan Hsu, Jean Pierre Locquet and Laura Bégon-Lours

Abstract: This work presents a characterization platform for comprehensive electrical testing of heterogeneously integrated oxide stacks, enabling simultaneous evaluation of multiple functional layers at different fabrication stages. The study focuses on the integration of ferroelectric hafnium zirconium oxide with vanadium oxide, a strongly correlated material exhibiting a metal insulator transition. The platform enables detailed analysis of how functional properties such as ferroelectric switching and correlated transport evolve during processing. Results reveal increased leakage in hafnium oxide and suppression of the metal insulator transition during crystallization, both with and without alumina oxygen blocking layers. Implemented using open source design and layout tools, this platform provides a powerful diagnostic and optimization framework for the integration of complex oxide materials, supporting the development of advanced ferroelectric and neuromorphic devices.

Authors : Ju Yong Park, Hyojun Choi, Jaewook Lee, Kun Yang, Sun Young Lee, Dong In Han, Intak Jeon, Chang Hwa Jung, Hanjin Lim b, Woongkyu Lee , Min Hyuk Park

Abstract: Molybdenum is considered a promising electrode material for Hf1-xZrxO2 films owing to its enhancing impact on ferroelectricity and dielectric constant. However, it poses significant limitations, such as high leakage current density and low endurance, which must be addressed to ensure its applicability in Hf1-xZrxO2-based memories. The insertion of a TiN interlayer has been proven to effectively reduce the oxidation of a Mo electrode and suppress the formation of oxygen vacancies in Hf1-xZrxO2 films, as confirmed by transmission electron microscopy (TEM) and X-ray photoelectron spectroscopy (XPS) studies. An optimized 6 nm-thick Hf0.3Zr0.7O2 film with a TiN interlayer exhibited a leakage current density below 10–7 A/cm² at 0.8 V and an equivalent oxide thickness of 0.49 nm, demonstrating its suitability for cell capacitors in dynamic random-access-memories (DRAM).

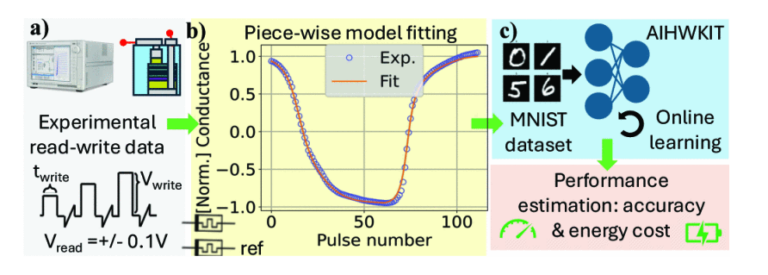

Title: Energy-convergence trade off for the training of neural networks on bio-inspired hardware

Authors : Nikhil Garg, Paul Uriarte Vicandi, Yanming Zhang, Alexandre Baigol, Donato Francesco Falcone, Saketh Ram Mamidala, Bert Jan Offrein, and Laura Bégon-Lours

Abstract:The increasing deployment of wearable sensors and implantable devices is shifting artificial intelligence processing toward extreme edge environments, requiring ultra low power for continuous operation. Inspired by biological neural systems, ferroelectric memristive devices offer a promising solution by enabling in memory computing and eliminating costly data transfers between memory and processing units. In this work, ferroelectric synaptic devices based on HfO2 ZrO2 superlattices are experimentally characterized and their measured weight update behavior is integrated into hardware aware neural network simulations. Results show that shorter programming pulses significantly reduce energy per update, although more training epochs are required. Despite this, total energy consumption is reduced without compromising classification accuracy. While standard stochastic gradient descent shows reduced accuracy due to asymmetric weight updates, a symmetry point shifting technique is introduced to compensate for this effect and restore performance. These findings highlight the fundamental trade off between energy consumption, convergence speed, and accuracy, demonstrating that optimized short pulse programming can significantly improve the efficiency of on chip learning in ferroelectric neuromorphic hardware.

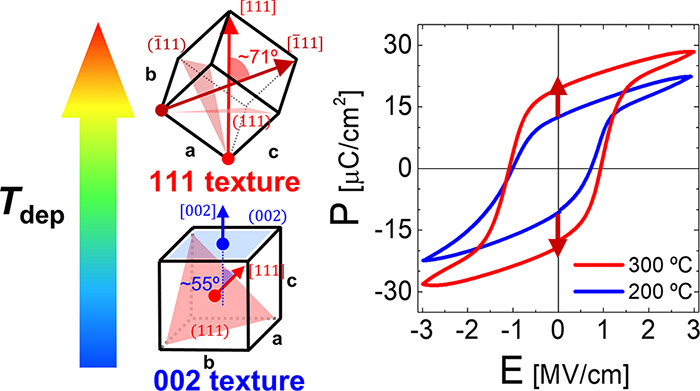

Authors : Dong Hee Han, Seung Yeon Kim, Hyun Woo Jeong, Younghwan Lee, Young Yong Kim, Woojin Jeon, and Min Hyuk Park

Abstract: The crystallographic texture of Hf0.5Zr0.5O2 (HZO) thin films plays a crucial role in determining their ferroelectric properties, requiring a deeper understanding of the texture transfer from the substrate. This study investigated the influence of the deposition temperature on the crystallographic texture, residual stress, and ferroelectric properties of HZO thin films. Grazing incidence wide angle X ray scattering analyses confirmed a pronounced increase in the {111} texture of the HZO films when the deposition temperature increased from 200 to 300 C. The observed {111} texture was attributed to the influence of thermodynamic stability on in situ nucleation and growth during atomic layer deposition at elevated temperatures, which led to preferential crystallization along the {111} direction. The improved {111} texture of the HZO film was shown to correlate directly with an approximately 25.0 percent increase in the remanent polarization Pr in positive up negative down measurements and an approximately 17.2 percent decrease in the Pr change during the wake up effect, reinforcing the superior performance of the films produced at higher temperatures.

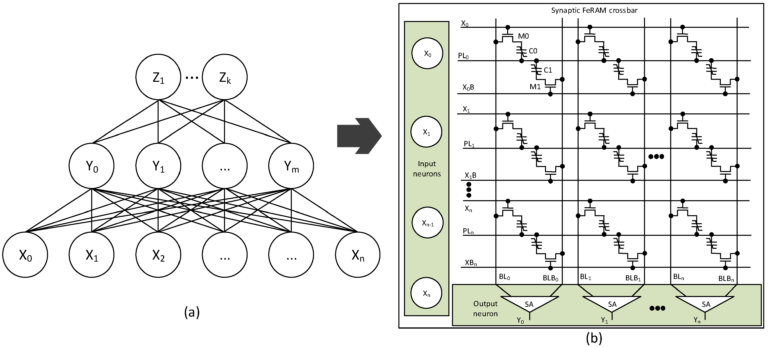

Title: Binary-Weighted Neural Networks Using FeRAM Array for Low-Power AI Computing

Authors : Seung Myeong Cho, Jaesung Lee, Hyejin Jo, Dai Yun, Jihwan Moon and Kyeong Sik Min

Abstract: Artificial intelligence AI has become ubiquitous in modern computing systems, from high performance data centers to resource constrained edge devices. As AI applications continue to expand into mobile and IoT domains, the need for energy efficient neural network implementations has become increasingly critical. To address this challenge, this work presents a binary weighted neural network BWNN architecture implemented using FeRAM ferroelectric RAM based synaptic arrays. By leveraging the non volatile nature and low power operation of FeRAM based computing in memory CIM, the proposed architecture achieves significant reductions in both dynamic and standby power consumption. Simulation results demonstrate that scaling the ferroelectric capacitor size reduces dynamic power by up to 6.5 percent, while eliminating DRAM like refresh cycles decreases standby power by more than 258 times under typical conditions. Furthermore, the combination of binary weight quantization and in memory computing enables energy efficient inference without significant loss in recognition accuracy, as validated using MNIST datasets. Compared to SRAM CIM, DRAM CIM, and STT MRAM CIM architectures, the proposed FeRAM CIM achieves superior energy efficiency, reaching 230 to 580 TOPS per watt in a 45 nm process. These results highlight the strong potential of FeRAM based BWNNs for energy constrained edge AI and IoT applications.

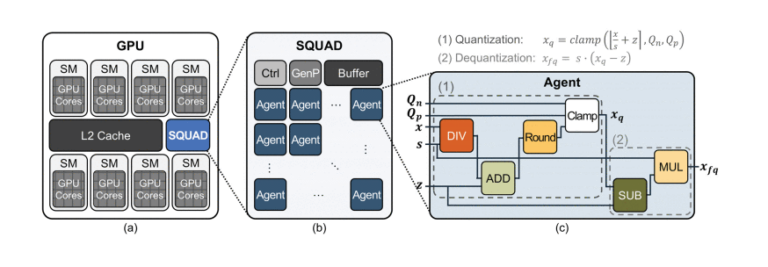

Authors : Ye Bin Kwon, Young Seo Lee, and Young Ho Gong

Abstract: Quantization aware training QAT is a key technique for maintaining neural network accuracy at extremely low bit precision such as 4 bit or lower. However, fake quantization operations introduce significant training time overhead compared to post training quantization. To address this challenge, this work proposes SQUAD, a scalable hardware accelerator designed to perform fake quantization operations with high performance and energy efficiency across multiple precision levels. The SQUAD architecture consists of multiple parallel and pipelined quantization accelerator cores with dedicated buffers and control units. Evaluation using ResNet, MobileNetV2, and DeiT models demonstrates that SQUAD reduces fake quantization latency by 93.1 percent and energy consumption by 97.6 percent compared to a commercial edge GPU. When integrated into edge GPU training workflows, SQUAD reduces forward pass latency by 48.8 percent and energy consumption by 51.2 percent. Overall, this results in a total training latency reduction of 14.6 percent and energy reduction of 15.3 percent, with only 0.43 percent hardware area overhead, highlighting its strong potential for energy efficient on device AI training.

Title: Ferroelectric NAND for efficient hardware bayesian neural networks

Authors : Minsuk Song, Ryun Han Koo, Jangsaeng Kim, Chang Hyeon Han, Jiyong Yim, Jonghyun Ko, Sijung Yoo, Duk hyun Choe, Sangwook Kim, Wonjun Shin and Daewoong Kwon

Abstract: The rapid advancement of artificial intelligence has enabled major progress in fields such as autonomous systems and medical diagnostics. However, conventional deterministic neural networks struggle to capture uncertainty, limiting their reliability when processing noisy, imbalanced, or incomplete real world data. Bayesian neural networks address this limitation by representing weights as probabilistic distributions, enabling uncertainty quantification and improved robustness. In this work, a 3D ferroelectric NAND based Bayesian neural network hardware system is proposed, leveraging incremental step pulse programming to achieve efficient and scalable probabilistic weight control. The intrinsic device to device variability and page level programming enable gaussian weight distributions in a single programming step without requiring structural modifications. By adjusting the programming voltage step, precise control over the weight distribution is achieved. The proposed system demonstrates effective uncertainty estimation, improved energy efficiency, and strong robustness to noise, highlighting the potential of ferroelectric memory devices for reliable and energy efficient neuromorphic computing.

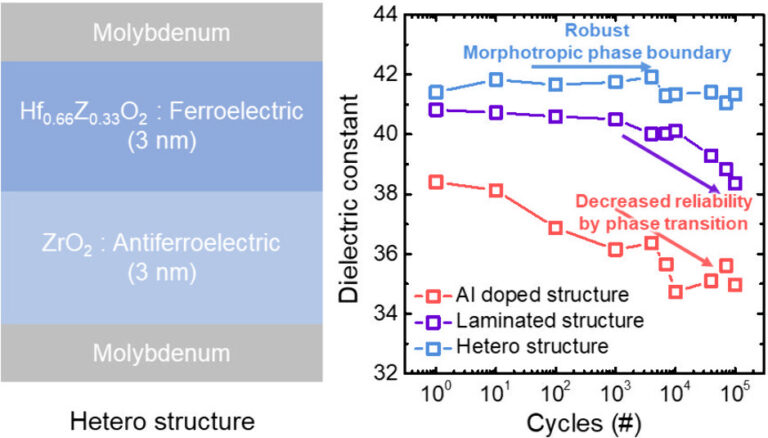

Authors : Changhyeon Han, Been Kwak, Joonhyeok Choi, Woojung Jeong, Rino Choi, and Daewoong Kwon

Abstract: This study investigates structural engineering strategies to suppress wake up effects in HfxZr1−xO2 HZO based metal ferroelectric metal capacitors exhibiting morphotropic phase boundary characteristics. Three configurations were analyzed, including Al doped, nanolaminated, and heterostructured HZO films. Depth profile X ray photoelectron spectroscopy and atomic force microscopy analyses revealed distinct differences in oxygen vacancy concentrations and grain sizes, which directly correlate with wake up behavior. The heterostructured HZO exhibited the lowest oxygen vacancy concentration at 2.49 percent and the largest average grain size of 7.5 nm, compared to Al doped HZO and laminated HZO. Due to its optimized defect distribution and improved grain morphology, the heterostructured HZO maintained stable phase composition even after 10^4 cycles, with minimal degradation in crystallinity and dielectric properties. These results highlight its strong potential for reliable and stable ferroelectric memory applications, particularly for high capacitance dynamic random access memory and neuromorphic computing systems.